Jedná se o relativně klidnou mezinárodní konferenci o superpočítačích na hardwarové frontě, přičemž obvyklé podezřelé neoznámily žádné nové procesory nebo přepínače ASIC. Zatímco Trish Damkroger, generální ředitelka divize vysoce výkonných počítačů Intel, přednesla hlavní slovo, které otevřelo ISC 2021, a poskytla trochu podrobnější pohled na procesor Xeon SP „Sapphire Rapids“ a akcelerátor GPU „Ponte Vecchio“, který má být představen příští rok, počínaje "Aurora" A21 exascale superpočítač v Argonne National Laboratory, většina posuvů a rychlostí těchto čipů zůstává záhadou.

Nikdo oficiálně neřekl, že stroj Aurora vyklouzl z revidovaného data dodání na konci roku 2021, ale to bylo podezření od doby, kdy Intel oznámil skluz ve svém 7 nanometrovém procesu, který se používá k leptání částí GPU Ponte Vecchio, známé také jako zařízení Xe HPC, loni v červenci.

V té době bylo plánem mít Auroru na poli v Argonne do konce roku 2021, ale to se zdálo nepravděpodobné vzhledem k tomu, že tehdejší generální ředitel Bob Swan řekl Wall Street, že počáteční dodávky Ponte Vecchio sklouznou do konce roku 2021. do začátku roku 2022. Intel revidoval plán Ponte Vecchio na použití směsi čipletů vyleptaných ve svých vlastních slévárnách i v slévárnách svých konkurentů, v tomto případě Taiwan Semiconductor Manufacturing Corp, která má na rozdíl od Intelu a GlobalFoundries ve skutečnosti fungující 7 nanometrový proces. (Samsung, jediný další dodavatel 7 nanometrových čipů a partner IBM pro Power10, na tom pracuje.)

Damkroger mimochodem nezmínil, že Intel ve skutečnosti posouvá datum dodání procesoru Sapphire Rapids Xeon SP, který je vyleptán pomocí vylepšení Enhanced SuperFin 10 nanometrového výrobního procesu Intelu. Ale Lisa Spelman, generální ředitelka Xeon and Memory Group v nedávno reorganizovaném Intelu, zveřejnila blogový příspěvek vysvětlující zpoždění při dodání serverového čipu v srdci – tedy spíše prodloužené míše od dob GPU Ponte Vecchio. dělat většinu myšlení – systém Aurora. Nyní jak Sapphire Rapids, tak Ponte Vecchio uklouzly a zdá se vysoce nepravděpodobné, že by Argonne letos získal základní části systému.

V každém případě prokluz Sapphire Rapids ovlivňuje více zákazníků než prokluz Ponte Vecchio a nyní to vypadá, že Ponte Vecchio porazí Sapphire Rapids do pole.

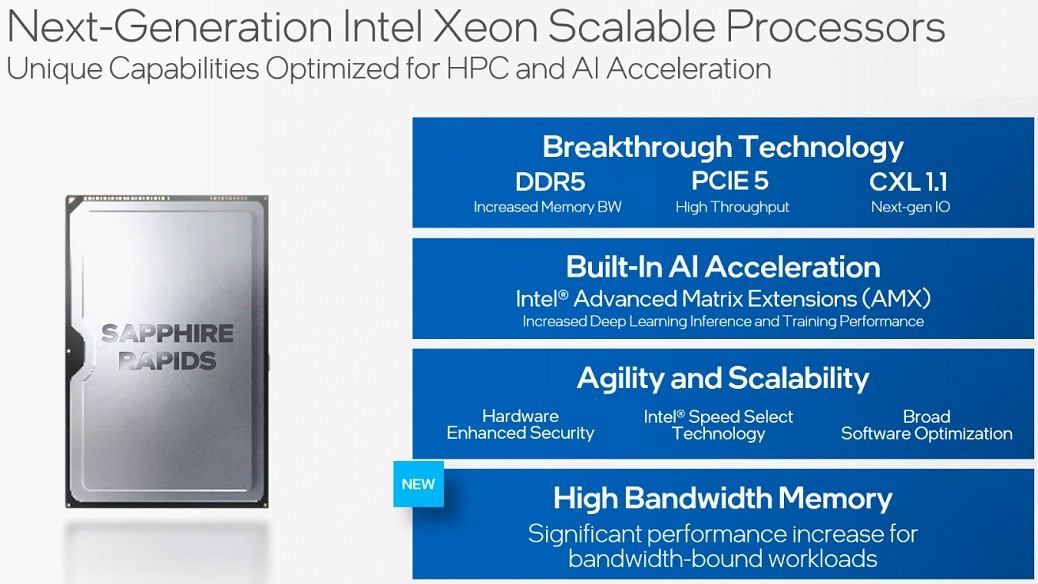

Čip Sapphire Rapids je založen na jádru „Golden Cove“, které má novou mikroarchitekturu, která zahrnuje dva nové akcelerátory, o kterých hovořil Spelman. První se nazývá Advanced Matrix Extensions nebo AMX a máme podezření, že jde o maticové matematické překrytí na vrcholu vektorových motorů AVX-512, které napumpuje výkon maticových operací podobných tomu, který provádějí jednotky Tensor Core na GPU Nvidia jako stejně jako maticové překryvy pro vektory v budoucích čipech IBM Power10. Spelman se na AMX nevrhá, ale říká, že na raném křemíku pro Sapphire Rapids běží vyvozování strojového učení a tréninková pracovní zátěž 2x rychleji než na současných procesorech Xeon SP „Ice Lake“, které mají pouze smíšenou přesnost ve svých vektorových motorech. zvýšit propustnost AI.

Další připravovaná funkce v jádře Golden Cove – alespoň varianta zaměřená na servery – se nazývá Data Streaming Accelerator nebo DSA a byla navržena pro různé druhy vysoce výkonných pracovních zátěží, aby se také zvýšil výkon streamovaných dat. jako transformační operace, které se často provádějí při streamování dat v úložných, síťových a analytických úlohách.

„Poptávka po Sapphire Rapids stále roste, protože zákazníci se dozvídají více o výhodách platformy,“ uvedl Spelman v oznámení na blogu. „Vzhledem k šíři vylepšení v Sapphire Rapids začleňujeme další dobu ověřování před uvedením do produkčního prostředí, což našim zákazníkům a partnerům zjednoduší proces nasazení. Na základě toho nyní očekáváme, že Sapphire Rapids bude ve výrobě v prvním čtvrtletí roku 2022 a rozjezd začne ve druhém čtvrtletí roku 2022.

Lidé v AMD se musí chichotat a hihňat. Pravděpodobně i ti z Ampere Computing. Už z dálky slyšíme vtipy „Sapphire Not So Rapids“ a „Ponte Vecchio Too Far“. . . .

Těžko říct, kdy měl nástupce současného „Ice Lake“ Xeon SP přijít na trh, protože samotné Ice Lake se tolik prohánělo. Ice Lake bylo odloženo asi o tři roky, když bylo spuštěno v březnu, takže to, co se stalo Sapphire Rapids, mělo posunout někam o 18 až 24 měsíců poté. Nazvěme to březen 2019, aby byl štědrý. To nyní znamená, že 10 nanometrové čipy jsou po tomto zpoždění stále tři roky pozadu a nebyly schopny je dohnat. Doufejme, že kvůli Intelu nedojde k dalšímu zpoždění s „Granite Rapids“ Xeon SP, který bude vyleptán 7 nanometrovými procesy. Po zpoždění v červenci 2020 procesory Granite Rapids Xeon SP sklouzly do první poloviny roku 2023 ve srovnání s očekávaným uvedením na začátku až do poloviny roku 2022. To je doba, kdy Sapphire Rapids nyní útočí.

Velkým odhalením na ISC 2021 bylo, že bude k dispozici varianta procesoru Sapphire Rapids zaměřená na pracovní zátěže HPC a AI, která bude zahrnovat paměť HBM. „Sapphire Rapids vyjde dříve než Sapphire Rapids s HBM, ale zhruba ve stejném časovém rámci,“ říká Damkroger. „A kdokoli si bude moci koupit Sapphire Rapids s HBM. HBM můžete použít samostatně, nebo jej můžete použít s DRAM.“ To je vskutku zajímavý vývoj. A jak řekl Damkroger, nepůjde pouze o speciální SKU, které si mohou koupit pouze vybraní zákazníci. Otázkou je, co bude přídavek HBM stát a kolik výkonu přidá.

O tom, jak bude Sapphire Rapids s HBM vypadat, kolují nějaké zvěsti, jednu z nich můžete vidět zde a zdá se být docela pravděpodobná. Tato zpráva říká, že čip Sapphire Rapids má čtyři 15jádrové dlaždice pro výpočet, přičemž jedno jádro je deaktivováno, pravděpodobně pro zvýšení efektivního výnosu. Maximální počet jader na patici tedy bude čtyřikrát čtrnáct nebo 56 jader, s možným skokem na 60 jader, pokud se výtěžnost 7 nanometrů zlepší.

Tento přístup je přesně to, co IBM dělá se svým čipem Power10, který má 16 fyzických jader a pouze 15 jader se aktivuje hned od začátku, protože vědí, že výnosy 7 nanometrového procesu společnosti Samsung budou – jak bychom to měli vyjádřit? ? - namáhavý. A než začnete, nezapomeňte, že s návrhy „Pascal“ a „Ampere GPU“ Nvidia udělala totéž se 7 nanometrovými procesy TSMC.

Není jasné, zda jsou tyto patice Sapphire Rapids vyrobeny z čipů, což by znamenalo mít I/O a paměťové řadiče oddělené od bloků jádra, nebo zda se jedná o celé CPU, které jsou implementovány vícečipovým způsobem, jak to udělala AMD s „Naples“ Epyc 7001 a dřívější Opterony už dávno a jak to IBM dělá od Power5 v roce 2005. Existují čtyři zásobníky HBM2, takže všechny mohou mít vlastní paměť a může to být MCM, pokud je tato zpráva správná . Hromady HBM2 jsou čtyři vysoké s kapacitou 16 GB, celkem tedy 64 GB na socket. A to je naprosto rozumné množství hlavní paměti pro aplikace HPC a AI a při šířce pásma 1 TB/s je to také docela rozumné. Myslíme si, že kapacita HBM by mohla být zdvojnásobena na 128 GB docela snadno, ale ne levně, s osmi vysokými zásobníky. Není jasné, kolik paměti DDR5 bude tento socket Sapphire Rapids adresovat, ale pravděpodobně to bude alespoň 512 GB a pravděpodobně 1 TB a možná dokonce 2 TB.

Očekává se, že špičkové čipy Sapphire Rapids budou vážit 400 wattů, včetně jejich paměti HBM2. Už dávno jsme vtipkovali, že veškerá výpočetní technika bude z dlouhodobého hlediska vypadat jako grafické karty. To jistě platilo pro Fujitsu A64FX a procesory NEC Aurora používané v HPC (to je jiná Aurora) a z dlouhodobého hlediska můžete očekávat i HBM variantu Epyc. To by ve skutečnosti mohlo být jedním z tajemství exascale systémů, které jednotka Cray společnosti Hewlett Packard Enterprise buduje pro americké ministerstvo energetiky.

Už víme, že Intel a HPE/Cray používají dvoupaticový uzel Sapphire Rapids se šesti akcelerátory Ponte Vecchio GPU propojenými přes sběrnici PCI-Express 5.0 pomocí protokolu CXL 1.1 k CPU. Tři GPU na CPU, stejně jako v superpočítači „Summit“ v Oak Ridge National Laboratory postaveném společnostmi IBM a Nvidia.

GPU akcelerátor Ponte Vecchio Xe HPC, zobrazený na hlavním obrázku v horní části tohoto příběhu, má 49 dlaždic a více než 100 miliard tranzistorů. Podle Damkrogerové je to bestie a byla zapnuta a raný křemík prochází testováním a ověřováním a také zmínila další tvarové faktory, které budou k dispozici, jak můžete vidět výše. K dispozici je čtyř GPU subsystém, jak je znázorněno, založený na Open Compute Project’s Open Accelerator Module, stejně jako osm GPU subsystém, který není zobrazen, který pravděpodobně také odpovídá specifikaci OAM. Pravděpodobně budou mít koherentní rozhraní přes CXL mezi GPU a ven do CPU pomocí přepínací struktury PCI-Express 5.0.

PREV: Zákon o 35 petabajtech All-Flash Balancing Act

NEXT: Google provádí serverovou matematiku s instancemi Tau Cloud